Universidad de Concepción Dirección de Postgrado Facultad de Ingeniería -Programa de Magíster en Ciencias de la Computación

# DETECCION DE PATRONES GEOMETRICOS MEDIANTE LA EXTRACCION DE SIGNATURE (GEOMETRIC PATTERN DETECTION USING SIGNATURE EXTRACTION)

## CRISTIAN ESTEBAN ANDRADES MUÑOZ CONCEPCIÓN-CHILE 2015

Profesor Guía: Andrea Rodríguez Tastets Dpto. de Ingeniería Informática y Ciencias de la Computación, Facultad de Ingeniería Universidad de Concepción

# DETECCIÓN DE PATRONES GEOMÉTRICOS MEDIANTE LA EXTRACCIÓN DE *SIGNATURE*

## (GEOMETRIC PATTERN DETECTION USING SIGNATURE EXTRACTION)

$\operatorname{por}$

Cristian Esteban Andrades Muñoz

Patrocinante: Andrea Rodríguez T

Tesis presentada para optar al Grado de

MAGÍSTER EN CIENCIAS DE LA COMPUTACIÓN

Departamento de Ingenería Informática y Ciencias de la Computación

UNIVERSIDAD DE CONCEPCIÓN

Concepción, Chile Octubre, 2013

## Acknowledgments

En primer lugar quisiera agradecer a la comisión evaluadora de este trabajo de tesis, Nancy Hitschfeld y Leo Ferres. Igualmente, agradecer a Synopsys Inc. y al Dr. Charles Chiang por su valioso aporte y orientación como experto en el área. Particulares agradecimientos al docente guía de esta investigación, Andrea Rodríguez, por su apoyo, paciencia, y formación tanto académica como personal. Finalmente, a mi pareja y pilar, Mariana Soto, por estar ahí en cada momento.

## Resumen

En la evolución constante de los procesos de manufactura de circuitos, la detección de configuraciones conflictivas se ha convertido en una tarea crucial en el proceso de diseño y producción. Estas configuraciones pueden provocar fallos en el circuito pues son propensas a sufrir distorsiones en las etapas de fabricación, ya sea por efectos de estrés de materiales, baja tolerancia a procesos de impresión como la fotolitografía, entre otros. La investigación en torno a esta problemática ha dado lugar a diferentes enfoques y técnicas que se utilizan para obtener soluciones eficaces que permitan a los diseñadores, ya sea a evitar el uso de configuraciones conflictivas, como a corregirlas o eliminarlas cuando aparecen en un diseño tras el uso de herramientas automatizadas. El problema de fondo es que estas técnicas, que suponen un coste adicional en el proceso de diseño, no siempre son eficaces, sobre todo desde el punto de vista de tiempos de ejecución.

El siguiente trabajo de tesis de magister amplía el trabajo realizado para la obtención de mi título profesional de Ingeniero Civil Informático. En dicho trabajo, se extrae cierta información relevante de regiones rectangulares de un diseño o *layout*. Esta información, llamada *signature* o firma de la región, es posteriormente utilizada para decidir si una región contiene o no una cierta configuración que se desee eliminar. Típicamente, estas configuraciones corresponden a patrones geométricos que, dados los procesos de manufactura, tienen una alta probabilidad de dar origen a una falla, conocida como *hotspot*. En otras palabras, un *hotspot* es una configuración de componentes electrónicos que provoca un mal funcionamiento del circuito. De forma adicional, este trabajo refina el trabajo anterior respecto a la estructura de datos utilizada, redefine la *signature* para patrones que tengan una dimensión distinta a la ventana de análisis, y realiza una evaluación exhaustiva de tiempo y calidad de los resultados. El objetivo principal de este método es reducir los tiempos de ejecución necesarios en las etapas de detección de *hotspots* al disminuir las porciones del diseño que deben ser analizadas usando técnicas más complejas. Para ello se utilizan algoritmos que transforman representaciones geométricas expresadas como reglas espaciales a representaciones expresadas como grafos dirigidos, los que son finalmente utilizados para obtener representaciones vectoriales de dichas representaciones geométricas. Estas representaciones vectoriales, denominadas la *signature* de un patrón geométrico, son almacenadas en estructuras indexadas para permitir posteriores búsquedas en base a índices. El trabajo presenta evaluaciones experimentales de diversas estructuras indexadas basadas en arboles binarios de búsqueda, tablas hash, y combinaciones de ambos tipos. Los experimentos muestran tiempos de ejecución que permiten disminuir los tiempos de ejecución que actualmente se requieren para la detección de patrones en diseños de circuitos integrados, así como uso de memoria que permiten la ejecución del proceso en computadores personales. Las estructuras que utilizan una combinación de estructuras indexadas mostraron ser la que ofrecen la mejor relación entre tiempos de ejecución y memoria requerida.

## Abstract

Due to the constant improvement of the circuit manufacturing technology, the detection of conflictive configurations has become relevant, being an important part of the design and production process. These conflictive configurations can lead to circuit failures, which can be produced due to a series of factors that can generate distortions at manufacturing stages. These factors can be, for example, the stress of materials, low tolerance to printing processes as photolithography, among others. The investigation around this problem has given rise to different approaches and techniques used to obtain effective solutions, which allow the designers to avoid the use of conflictive configurations, or correct or remove them when they appear in a design after the use of automated tools. The background problem is that these techniques, which suppose an additional cost to the design process, are not always efficient, mostly from time point of view.

## $\mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x}$

This Master's thesis improves and extends the work done to obtain the professional title of *Ingeniero Civil Informático*. It extracts some selected information, referred as *signatures*, from rectangular regions of a circuit design or *layout*. These signatures are then used to decide if a region contains or not a configuration that want to be removed. Typically, these configurations correspond to geometric patterns that, due to the manufacturing process used to build an IC, have a high probability to become a failure, which is known as *hotspots*. In other words, a *hotspot* is an electronic component configuration that causes a malfunction in the circuit. Additionally, this work refines the previous work regarding the data structure used, redefines the *signature* for patterns having different size with respect to the window of extraction, and makes a comprehensive evaluation of time and quality of results. The principal objective of this method is to reduce the time cost of the *hotspot*-detection process by filtering out portions of the layout that need to be analyzed using more complex techniques.

To achieve this objective, some algorithms are used. These algorithms transform

a spatial-rule representation of a geometric pattern into an oriented-graph representation, which are finally used to obtain a vectorial representation of the geometric pattern. This vectorial representation, called the *signature* of the geometric pattern, are stored in a indexed structure that allows later lookups based on indexes. This thesis work presents an empiric evaluation of various different indexed structures based on binary-search trees, hash tables, and combinations of both types. The experiments show execution times that allow to reduce the execution times currently needed to detect geometric patterns in integrated circuit designs, as well as the memory required allows to operate the process in personal computers. The data structures that use a combination of indexed structures have shown to be the ones that offer the better balance between execution times and memory used.

## Table of Contents

| Ackno   | wledgments                                                   | ii        |

|---------|--------------------------------------------------------------|-----------|

| Resum   | len                                                          | iii       |

| Abstra  | let                                                          | v         |

| List of | Tables                                                       | ix        |

| List of | Figures                                                      | x         |

| Chapte  | er 1 Introduction.                                           | 1         |

| 1.1     | Background                                                   | 1         |

| 1.2     | Motivation                                                   | 3         |

| 1.3     | Hypothesis                                                   | 4         |

| 1.4     | Objectives                                                   | 4         |

| 1.5     | Methodology.                                                 | 5         |

| 1.6     | Organization.                                                | 5         |

| Chapte  |                                                              | 6         |

| 2.1     | Lithography simulation.                                      | 6         |

| 2.2     | Detection using pattern recognition                          | 10        |

| 2.3     | Detection using machine learning techniques                  | 15        |

| 2.4     | Graph-oriented detection.                                    | 20        |

| Chapte  | er 3 Signature-based indexing and searching.                 | <b>23</b> |

| 3.1     | Signature.                                                   | 24        |

| 3.2     | Design layout representation and <i>signature</i> extraction | 27        |

| 3.3     | Pattern representation and <i>signature</i> extraction       | 31        |

| 3.4     | Signature-based searching.                                   | 42        |

|         |                                                              |           |

| Chapter 4    |        | Experimental evaluation.                                                    | 49 |

|--------------|--------|-----------------------------------------------------------------------------|----|

| 4.1          | Datase | et                                                                          | 49 |

| 4.2          | Memor  | ry hierarchy in the efficiency of <i>signature</i> extraction from layouts. | 52 |

|              | 4.2.1  | Layout preprocessing using a single scope                                   | 52 |

|              | 4.2.2  | Layout preprocessing using differentiated scopes                            | 55 |

|              | 4.2.3  | Layout preprocessing using pivots.                                          | 59 |

| 4.3          | Indexi | ng structures                                                               | 64 |

|              | 4.3.1  | Using a binary search tree                                                  | 65 |

|              | 4.3.2  | Using two binary search trees                                               | 69 |

|              | 4.3.3  | Using has functions                                                         | 71 |

|              | 4.3.4  | Space cost using hash table                                                 | 79 |

|              | 4.3.5  | Space cost using hash table plus binary search tree                         | 83 |

| 4.4          | Search | ing patterns in the layout.                                                 | 86 |

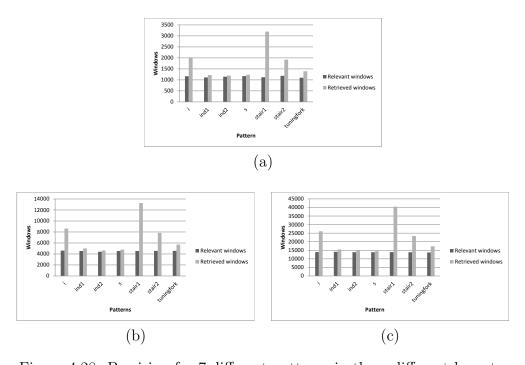

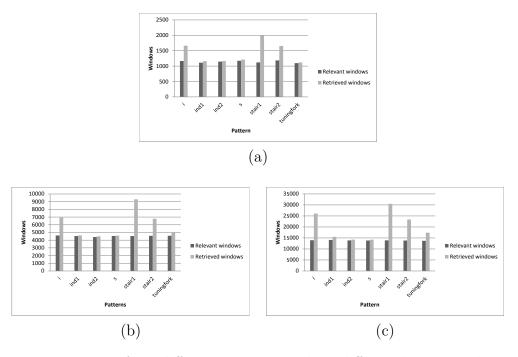

|              | 4.4.1  | Searching with pattern and window of the same size                          | 88 |

|              | 4.4.2  | Searching with pattern and window of different size                         | 90 |

| Chapte       | r 5    | Conclusions and future research directions.                                 | 93 |

| Append       | lix A  | Range patterns.                                                             | 94 |

| Bibliography |        |                                                                             | 96 |

|              |        |                                                                             |    |

## List of Tables

| 3.1 | Matrix of pairs of <i>range graph</i> partitions | 48 |

|-----|--------------------------------------------------|----|

| 3.2 | Matrix of partitions: IDs displacement           | 48 |

| 4.1 | Experimental layouts: summary table              | 50 |

| 4.2 | Experimental range patterns: summary table       | 51 |

| 4.3 | Shared area between contiguous windows           | 59 |

| 4.4 | Accessing time cost table (in seconds).          | 89 |

| 4.5 | Algorithms time cost table (in seconds)          | 90 |

| 4.6 | Accessing time cost table.                       | 92 |

| 4.7 | Algorithms time cost table                       | 92 |

# List of Figures

| 1.1  | Examples of manufacturing variations. [19]                                                 | 2  |

|------|--------------------------------------------------------------------------------------------|----|

| 1.2  | Basic DRC checks. [4]                                                                      | 2  |

| 2.1  | Example of a lithographic simulation post-OPC for an $45 \text{ nm}$                       |    |

|      | design. $[20]$                                                                             | 9  |

| 2.2  | Extraction of <i>situations</i> . $[15]$                                                   | 10 |

| 2.3  | Construction of a MTCG graph. $[4]$                                                        | 12 |

| 2.4  | Binary matrix representation. $[6]$                                                        | 13 |

| 2.5  | Range pattern Rocket. [6] $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 14 |

| 2.6  | Cutting-slices of the rocket range pattern. [6]                                            | 15 |

| 2.7  | Critical features. $[20]$                                                                  | 16 |

| 2.8  | Feature extraction. [19]                                                                   | 17 |

| 2.9  | Geometrical metrics. [19]                                                                  | 18 |

| 2.10 | Representation based on geometries density. [23]                                           | 19 |

| 2.11 | CD variations induced by the interaction between geometries. [5]                           | 21 |

| 2.12 | Graph and dual graph representation. [5]                                                   | 21 |

| 3.1  | Regular and irre <mark>gular</mark> grid representation                                    | 26 |

| 3.2  | Example of a layout representation                                                         | 28 |

| 3.3  | Example of a simple layout                                                                 | 30 |

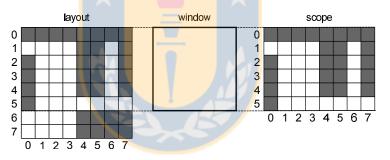

| 3.4  | Example of window creation                                                                 | 30 |

| 3.5  | Example of <i>signature</i> extraction for different windows                               | 31 |

| 3.6  | Three different <i>realizations</i> of the same representative pattern.                    | 32 |

| 3.7  | A range pattern specification.                                                             | 32 |

| 3.8  | Example of rectangles' boundaries distances                                                | 33 |

| 3.9  | Range graphs of the range pattern in Figure 3.7                                            | 35 |

| 3.10 | Four distance restrictions.                                                                | 35 |

| 3.11 | Example of an horizontal topological order                                                 | 38 |

| 3.12 | Definite HRG and VRG that derive an incompatible realization.                              | 39 |

| 3.13 | Different irregular grid realizations of <i>range pattern</i> in figure 3.7.       | 43 |

|------|------------------------------------------------------------------------------------|----|

| 3.14 | Inverted index for layout in Figure 3.3                                            | 43 |

| 3.15 | Example of a window and a sub-window                                               | 45 |

| 3.16 | Example of the splitting process of a horizontal $\mathit{range graph}$ .          | 47 |

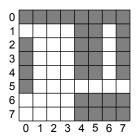

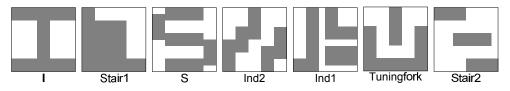

| 4.1  | Examples of experimental <i>hotspots</i> -patterns                                 | 51 |

| 4.2  | Example of a layout and a window size                                              | 53 |

| 4.3  | Example of a layout and its first scope                                            | 53 |

| 4.4  | Example of a layout and its second scope                                           | 54 |

| 4.5  | Example of a layout and its third scope                                            | 54 |

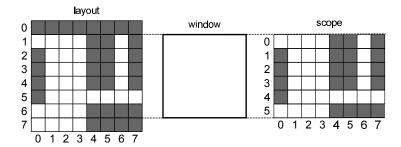

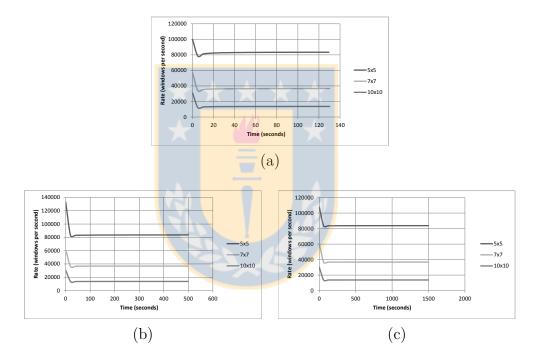

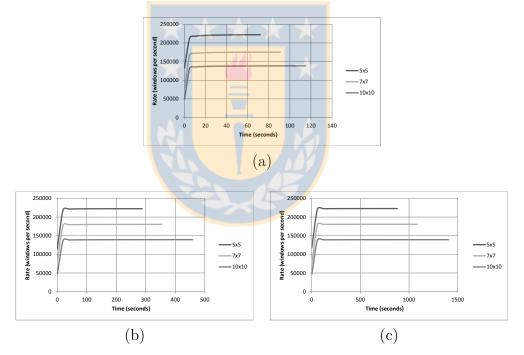

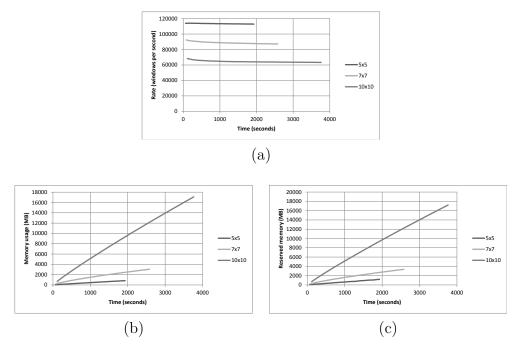

| 4.6  | Naïve extraction rates                                                             | 55 |

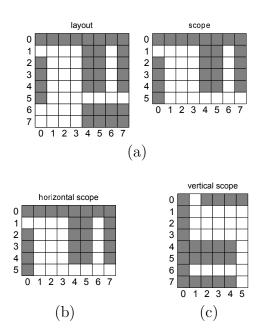

| 4.7  | One scope and its two scopes structures                                            | 57 |

| 4.8  | Naïve extraction rates using two scope structures $\ldots$                         | 58 |

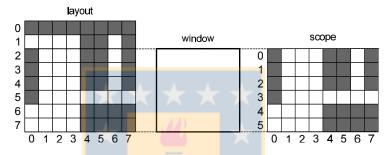

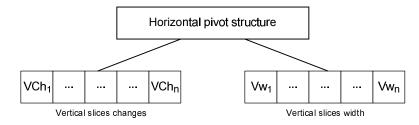

| 4.9  | Horizontal pivot structure representation                                          | 61 |

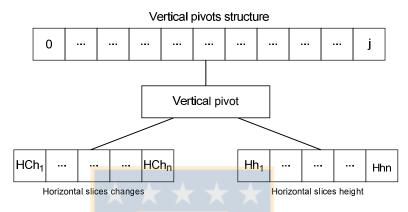

| 4.10 | Vertical pivots structure representation                                           | 62 |

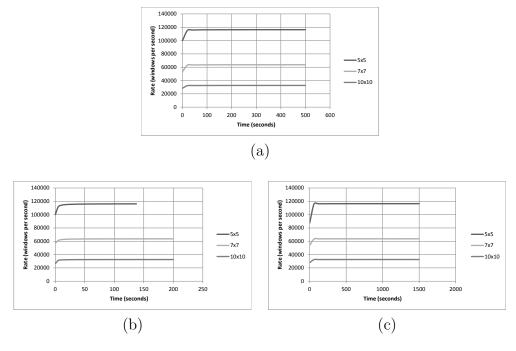

| 4.11 | Smart extraction rates using two scope structures and pivots                       |    |

|      | for $\mathcal{S}^+$ calculation.                                                   | 63 |

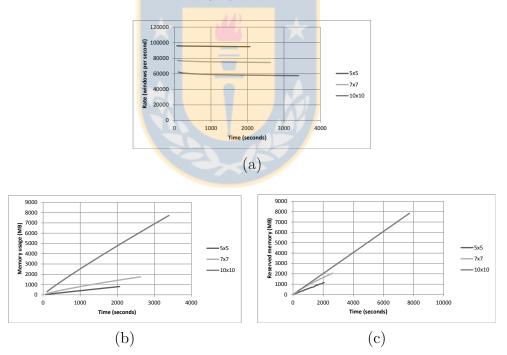

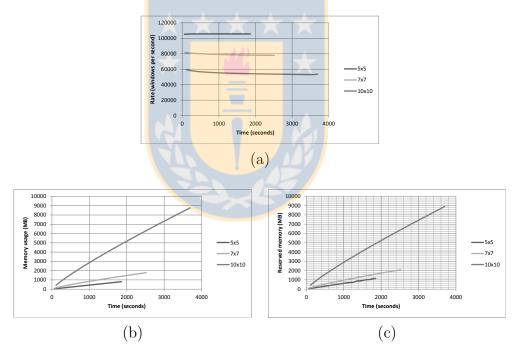

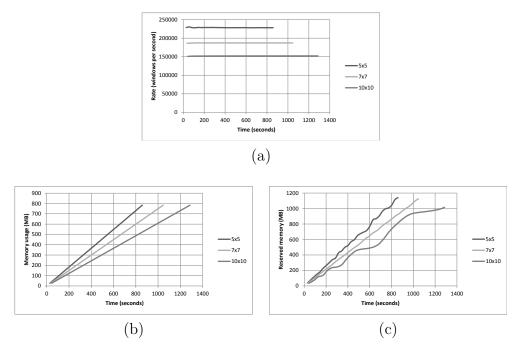

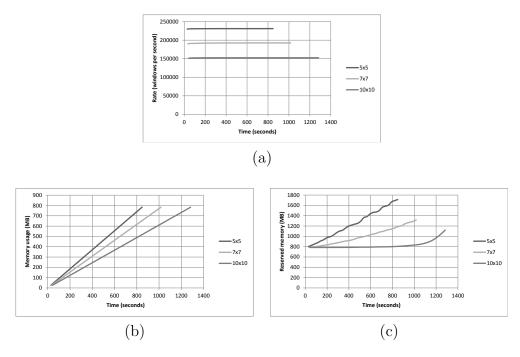

| 4.12 | MAP structure: Extraction and population, memory usage and                         |    |

|      | reserved memory over time.                                                         | 66 |

| 4.13 | MAP structure with initial reserved memory: Extraction and                         |    |

|      | population, memory usage and reserved memory over time                             | 68 |

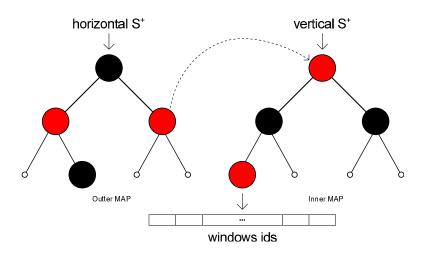

| 4.14 | Vertical pivots structure representation                                           | 70 |

| 4.15 | Dual-MAP structure: Extraction and population, memory us-                          |    |

|      | age and reserved memory over time                                                  | 70 |

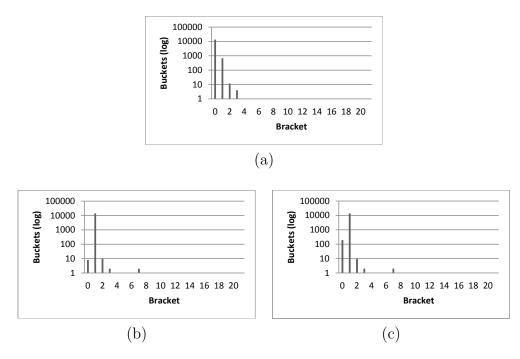

| 4.16 | Windows extraction over a $14.000 \ times 14.000$ layout: Win-                     |    |

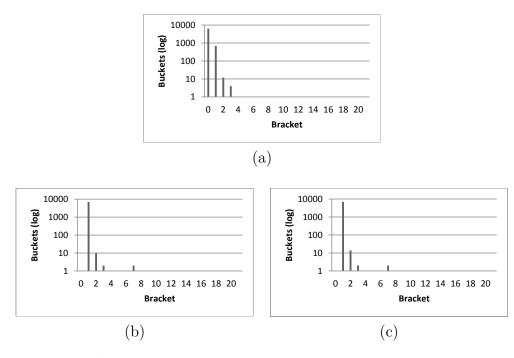

|      | dows per bucket histogram using a hash table of 7.000 buckets.                     | 75 |

| 4.17 | Windows extraction over a $14.000 \times 14.000$ layout: Different $\mathcal{S}^+$ |    |

|      | per bucket histogram using a hash table of 7.000 buckets                           | 76 |

| 4.18 | Zoom of the histogram of windows per bucket for the three                          |    |

|      | different hash functions.                                                          | 77 |

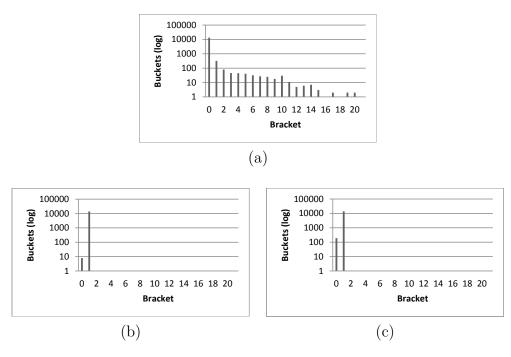

| 4.19 | Windows extraction over a $14.000 \ times 14.000$ layout: Win-                                                     |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | dows per bucket histogram using a hash table of 14.000 buckets.                                                    | 78 |

| 4.20 | Windows extraction over a $14.000 times 14.000$ layout: Different                                                  |    |

|      | $\mathcal{S}^+$ per bucket histogram using a hash table of 14.000 buckets.                                         | 79 |

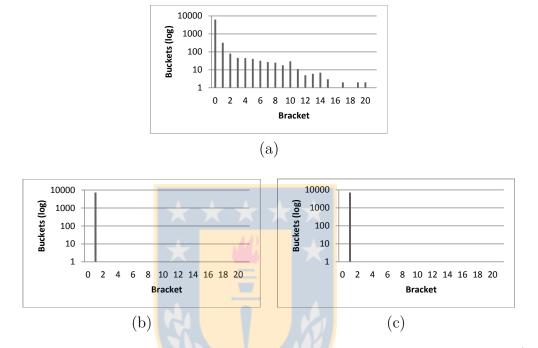

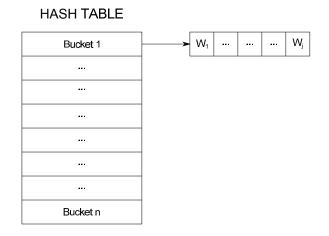

| 4.21 | Simply hash structure representation.                                                                              | 80 |

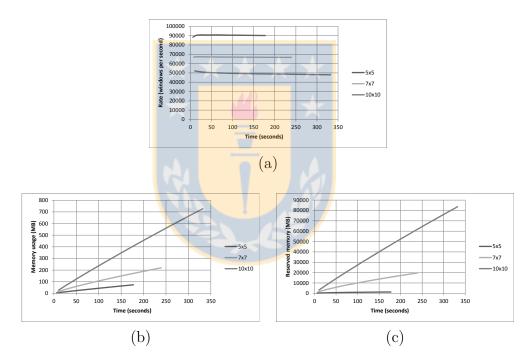

| 4.22 | Simply hash structure: Extraction and population, memory us-                                                       |    |

|      | age and reserved memory over time                                                                                  | 81 |

| 4.23 | Simply hash structure with initial reserved memory: Extraction                                                     |    |

|      | and population, memory usage and reserved memory over time.                                                        | 82 |

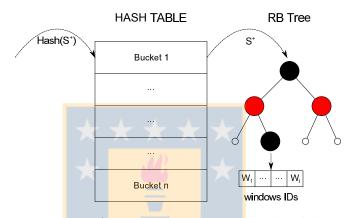

| 4.24 | Representation of a structure using a hash table and a binary                                                      |    |

|      | search tree.                                                                                                       | 83 |

| 4.25 | Hash table and binary search tree structure: Extraction and                                                        |    |

|      | population, memory usage and reserved memory over time                                                             | 84 |

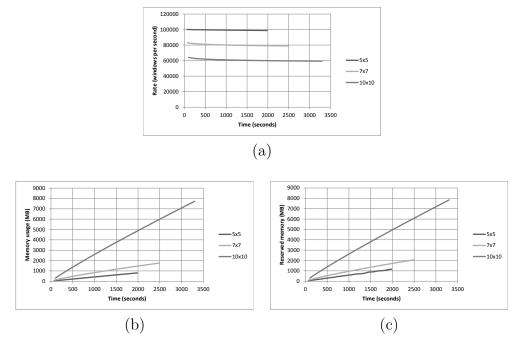

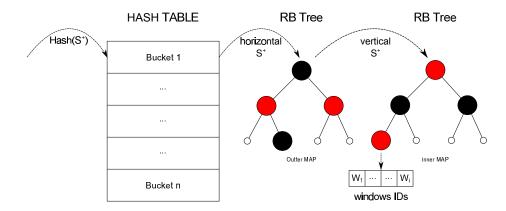

| 4.26 | Representation of a structure using a hash table and two binary                                                    |    |

|      | search trees.                                                                                                      | 85 |

| 4.27 | Hash table and dual binary search tree structure: Extraction                                                       |    |

|      | and population, memory usage and reserved memory over time.                                                        | 86 |

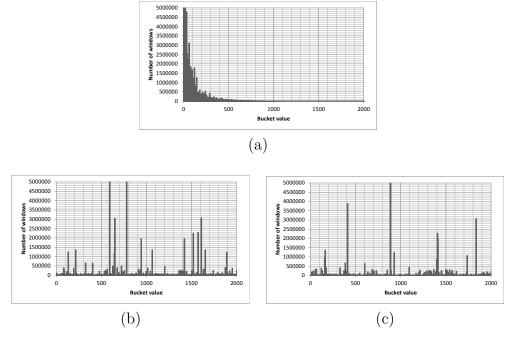

| 4.28 | Precision for 7 different patterns in three different layouts                                                      | 89 |

| 4.29 | Precision for 7 d <mark>ifferent patte</mark> rns in three different layouts with                                  |    |

|      | patterns larger than the windows of extraction                                                                     | 91 |

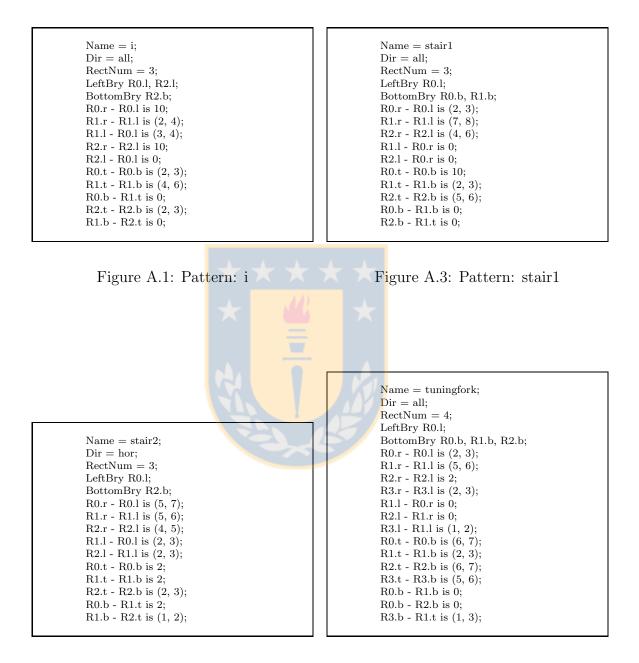

| A.1  | Pattern: i                                                                                                         | 94 |

| A.2  | Pattern: stair1                                                                                                    | 94 |

| A.3  | Pattern: stair1                                                                                                    | 94 |

| A.4  | Pattern: tuningfork                                                                                                | 94 |

| A.5  | Pattern: ind $1 \ldots \ldots$ | 95 |

| A.6  | Pattern: ind $2$                                                                                                   | 95 |

| A.7  | Pattern: s                                                                                                         | 95 |

## Chapter 1

## Introduction.

#### 1.1 Background.

A typical integrated circuit or IC is built in a chip, creating layers of different materials such as metal or polysilicon<sup>1</sup>. Geometrical patterns are then printed on these layers using different printing techniques, giving rise to electrical components whose interactions will define the circuit behavior. Designing a circuit requires to have knowledge about the interaction between layers for a certain manufacturing technology, as well as the limitations that these manufacturing processes impose.

The principal objective of a designer is to put as many electrical components in the less area as possible, achieving a correct circuit behavior. A good example of what is an IC is a microprocessor for which it is very important the amount of information that can be processed and the processing speed of the microprocessor. Because the enormous quantity of electrical and wire components needed to build an IC, the schematization problem, known as *layout problem*, becomes relevant.

Current technology for nanoscale IC construction has certain problems inherent in the manufacturing process that require special attention from designers. As going through the circuit design process that involves determining which pattern will be included in a design, in which layer and position they will be included, and do so trying to make a design as compact as possible, designers have to prevent the appearance of *hotspots*. The prevention can be achieved by detecting the occurrence of conflictive patterns in a design, and correcting or removing them before the design goes to production. This detection becomes critical below the 90 nanometers technology [13] as a reason of printing problems that cause variation between a design and its physical circuit, such as focus fixation or light exposure in the photolithography process. These variations can lead to *bridging* between electrical components, and *necking* or *line-end*

<sup>&</sup>lt;sup>1</sup>Also called Polycrystalline silicon.

shortening in its dimensions when they are printed (see figure 1.1). These anomalies cause the circuit to fail in contrast to some of the specifications under which the circuit was designed, reason why they are known as *yield detractors* or *hotspots*.

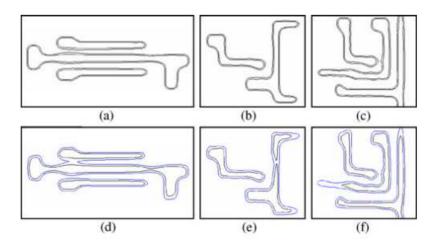

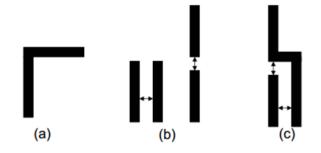

Figure 1.1: Examples of manufacturing variations. [19] (a)-(d) Bridging, (b)-(e) Necking, (c)-(f) Line-end shortening.

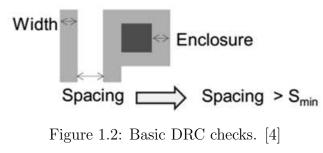

Design-rule checking (DRC) was introduced as a first attempt to help designers to detect and avoid *hotspot* occurrences in designing stages. DRC is a major step during physical verification signoff of the design, where the designer defines a set of geometric restrictions and connectivity rules, known as *Design Rules*, that the circuit must satisfy (see figure 1.2). These rules seek to ensure sufficient margins according to the variability in the printing processes, reason why they are specific to a certain manufacturing process and may not be generalizable.

Width, spacing, and enclosure.

What is common is that, with the advance of manufacturing technology, the number of necessary rules, and its combinatorial explosion due to the significant increase of elements in a circuit, have increased the complexity of this technique. A standard practice is to reduce the rule number relaxing the set. This means to pass over some complex rules, which reduces the complexity of the verification process as expenses of yield. This decision may cause that some potential *hotspots* be overlooked, especially when the conflicting interactions are not local. For this reason, new complementary techniques were introduced. Some of them take into account local interactions, while others are capable of taking into account more global interactions.

These techniques suppose a high additional cost in the verification process, especially due to the dimensions of current designs and the density of components that the new technologies allow, increasing the apparition of potential *hotspots* and, therefore, the patterns that must be detected.

#### 1.2 Motivation.

Semiconductor fabrication plants, commonly called *fabs*, usually use design rules to represent process-*hotspots* and a typical design rule checker to detect such *hotspots*. However, this representation has been found to be inadequate [6], so the last few years there has been extensive work in the area of fast process simulation to aid DRC during the physical design stages. For example, industry has been using lithography *hotspot*detection processes based on aerial image simulators [22, 16]. The problem is to find new techniques that complement verification techniques that are currently used by *fabs*, at a low computational cost, usually measure in terms of runtime.

A previous work in [3] defined signatures to pre-filter regions of a layout from a *hotspot*-detection process. These signatures consist in some summarized information of a portion of the layout. Once the *signature* is obtained and stored, it is then used to decide if the portion of the layout contains or not a certain pattern to be identified. This identification process is used to modify or remove these patterns to avoid the occurrence of yield detractors or *hotspots*. The experiments shown in [1] laid the theoretical basis on which it is asserted that the use of signatures is a viable technique that allows this decision with a low rate of false positive. However, the proposed method still had various limitations and improvements to be done. Of particular interest are a more detailed *signature* extraction process and a study of

different storage structures. Additionally, a rather simplistic limitation was the fact that to obtain good results in terms of accuracy (i.e., low rate of false positive), the pattern to be searched should match the size of the portions or windows upon the signatures were extracted. This limitation means that the method was practically unusable in production processes because it is really very difficult and unrealistic to know the dimensions of a potential *hotspot* beforehand. Even more, the dimensions of same patterns could vary as printing technologies do.

#### 1.3 Hypothesis.

The hypothesis of this work is that it is possible to construct a *signature* that characterizes a certain configuration of geometries (from now the pattern), and use that *signature* to decide if this configuration is or is not contained in a certain area of a circuit design. To use this *signature* in a realistic situation, it must allow the decision even if the size of the pattern and the area of design are not exactly the same. It also must allow the detection of patterns even if there are rotations between the pattern and the design region.

#### 1.4 Objectives.

The objectives of this thesis are:

- 1. Define a *signature* over configurations composed of rectangular geometries. These configurations can be patterns or portions of layouts. The computation of these *signature* should consider time, and as a second priority, space costs.

- 2. Design an indexing structure that stores *signatures* and the identification of portions of a layout that match the signatures.

- 3. Design a search method over the indexing structure that use the *signature* of a pattern as a search key.

- 4. Perform an experimental evaluation of the quality of the *signature*, the time and space cost of the indexing structure and the time cost of the search process.

#### 1.5 Methodology.

The methodology followed by this work can be summarized in three basic steps that aim to answer the following questions: How the *hotspot* detection is addressed today? How can we contribute to improve the efficiency on the *hotspot*-detection process?, and How can we evaluate our contribution?

The first step is to present a review of the problem, determining the principal approaches in the state-of-the-art and their limitations. From this review, we can determine some useful elements to be used in our work, delimiting the contribution. From this first step, we chose approaches that result to be more similar to our previous done work in [1]. The review include works found in abstracts, papers and patents published in academic and commercial journals, bibliographic databases, and Internet search engines.

The next step is to propose a *signature*-based preprocessing and searching to filter out portions of a layout from *hotspot*-detection process. This includes to propose a data model to represent layouts and patterns and to design an indexing structure.

The last step is to determine the data analysis to be performed and what the evaluation criteria are. This step needs to set up the experimental evaluation to measure the evaluation criteria. Because a standard data analysis method has not been established nor decided yet from companies engaged in the area of this investigation, we use typical measurement form information retrieval and execution time criteria. These evaluations were performed by using our own implementations because more sophisticated analysis tools are typically distributed under paid licenses and need to be calibrated to a certain production process.

#### 1.6 Organization.

The organization of this document is as follows. Chapter 2 provides a brief review of related works, presenting techniques for *hotspots* detection that are used today, and resuming the contribution of this master thesis. Chapter 3 discusses the experimental evaluation, its results and conclusions, while the final chapter closes the work with general conclusions and future research directions.

## Chapter 2

## Related works.

In the literature we can distinguish four approaches for *hotspots* detection, each of them with its advantages and disadvantages. These four approaches are the *hotspot* detection using lithography simulation, the *hotspot* detection using pattern recognition, the *hotspot* detection using learning machine, and the *hotspot* detection using graph-oriented techniques. In this chapter we present a brief review of these approaches.

#### 2.1 Lithography simulation.

The real process of printing an IC involves more than only the design and the wafer, which is the surface where the IC is printed. As was said before, an IC is built layer by layer which are superposed obtaining a third-dimensional product from bi-dimensional representations. These representations include geometric shapes and are known as the design. Typically, the designs are constructed using CAD<sup>1</sup> tools and are used to build what is known as *mask*. A mask is used in the photolithographic process to print the design on the wafer.

As we can see in [12], to build a layer it is necessary to deposit material over a silicon layer and then remove part of it. The deposition process typically used a method called *Chemical Vapor Deposition* (CVD), while the removing process typically uses etching substances, leaving exposed some areas of a layer. To do this etching process, it is necessary to ensure that the areas that want to be maintained will not be etched by the acid. This is achieved by reinforcing the materials using light, from which this process receives the name of photolithography. A material known as photoresist is used and some regions are exposed to light. The areas with incidence to light can become resistant to the acid or soluble to it. In this way, geometrical shapes can

<sup>&</sup>lt;sup>1</sup>CAD stands for Computer Aided Drafting

be printed on a layer. The problem is that current dimensions of components are smaller than the frequency of the light used in this process. Because of this reason, the light should pass through a lens and mask that filter out the light exposition in some regions of the layer.

The resolution of a process of optical lithography, i.e., the ability to project a clear image of a small feature on the wafer, is limited by the wavelength of light and the numerical aperture (NA) of the reducing lens used for light exposure [7, 8]. As the minimum widths in Ultra Large Scale Integrated (ULSI) circuits reach resolutions smaller than 90nm, the difficulty of achieving high fidelity printing circuits increases, even when the NA significantly increases and the wavelength decreases [5].

The minimum width of the features that a projection system can print is given approximately by the formula 2.1, where CD corresponds to the minimal width that can be achieved while printing onto the wafer,  $k_1$  corresponds to a coefficient that encapsulates different factors related to the photo-lithographic process (usually varies between 0, 3 and 0, 4), NA corresponds to the NA of the lens view from the wafer, and  $\lambda$  is the wavelength of the light.

$$CD = k_1 \cdot \frac{\lambda}{NA} \tag{2.1}$$

Formula 2.1: Critical dimension of the features printed by a projection system.

Currently, laser light with wavelength between 248 nm and 193 nm are used. Photolithographic processes for low minimum widths require narrow margins for focus and exposure, resulting in high optical proximity effects as deviations in the critical dimensions of the prints [9]. These difficulties have led to the semiconductor industry to use complex conditional rules and recommended rules for specifying geometric constraints in the design stages [11], Resolution Enhancement Technology (RET) techniques, Optical Proximity Correction (OPC) [9].

OPC is a photolithography enhancement technique commonly used to compensate image errors due to diffraction or process effects. It is mainly used in the semiconductor industry due to the limitations of light techniques to maintain a correct edge placement, relative to the original design, into the etched image on the silicon wafer. These projected images appear with irregularities such as line widths that are narrower or wider with respect to the design. The irregularities can be compensated by changing the geometries on the mask used for imaging, and here is when OPC is used. OPC corrects these errors by moving edges or adding extra polygons to the pattern written on the mask or *photomask*. This may be driven by pre-computed look-up tables based on width and spacing between features, known as *rule based OPC*, or by using compact models to dynamically simulate the final pattern and thereby drive the movement of edges, typically broken into sections to find the best solution, known as *model based OPC*. The objective is to reproduce, as well as possible, the original layout drawn by the designer in the silicon wafer. This is achieved through iterative design modifications that are usually based on rules or models of the manufacturing process used by the *fab*.

Some process models have incorporated analysis and correction tools such as complete circuit simulators [14]. Although lithographic simulations generate accurate images of a design allowing robust verifications, these approaches have some limitations that make them hard to use in the practice [6].

- 1. Lack of information about subsequent processes, making it impossible to accurately model and calibrate some stages as OPC corrections. Moreover, simulations based on lithographic images usually detect regions that could be easily corrected by using masks-synthesis techniques, causing an over-estimation that slows the process of routing.

- 2. High computational cost of some models that are difficult to incorporate during physical designing stages, e.g., calculation of stress in metal components.

One approach that prevails today for *hotspots* detection is to predict them using a rigorous simulation post-OPC<sup>2</sup> along with customer-defined checks (see figure 2.1). Thereby, the configurations that don't meet the checks are marked or classified as *hotspots* and are corrected in accordance to this classification. Unfortunately, a complete simulation of an entire circuit design is computationally expensive, increasing greatly the time a circuit passes from the design stages to the production stages.

<sup>&</sup>lt;sup>2</sup>OPC stands for Optical Proximity Correction.

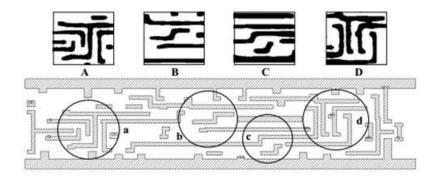

Figure 2.1: Example of a lithographic simulation post-OPC for an 45 nm design. [20] a, b, c and d are design views; A, B, C and D are lithographic simulations.

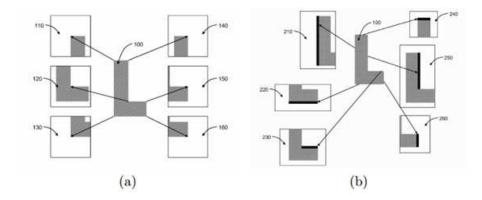

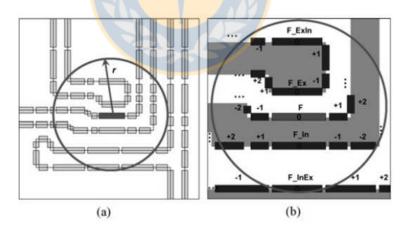

To overcome the cost of a full simulation, there are different techniques that aim to break up the complexity of this process. The work presented in [15] extracts situations of a design. A situation is a collection of shapes within a radius of extraction, which are described based on corners and edges. This generates a collection of figures among which may exist overlaps. These *situations* occur depending on some characteristics of the geometry to be analyzed, and can be used to improve OPC corrections. Figure 2.2 shows an example of the extraction of situations based on borders and a predefined radius. The radius could be expressed as Manhattan distance, Euclidean distance, among others, and typically corresponds to the radius of optical influence of the manufacturing tools. In the figure 2.2(a), the situations 110-116 are extracted from the polygon 100, based on corners and a r-Manhattan radius of extraction, which results in  $2r \times 2r$  square situations. Similarly, the figure 2.2(b) shows the situations based on borders for the same polygon and the same radius. This result in situations of  $2r + x \times 2r + y$ , where x is the length and y the height of the border around which the situation has been extracted. Interesting is to see that situations are described within a radius, and, therefore, are part of a larger geometry with its own characteristics. These situations are extracted in a hierarchical order, so that the design to be analyzed can be conceived as a partition of cells. The process traverses through this hierarchy of cells extracting a collection of geometries, where each cell instances can be seen as a cell instance of the cell in the top level.

Figure 2.2: Extraction of *situations*. [15] (a) corner based y (b) edge based.

The drawback of this approach is to define the situations and run simulations on each of them to make the necessary changes and then merge these situations to get the entire design again, but with the changes done. To avoid performing unnecessary simulations, the overlapping areas must be handled properly, and yet the separations of a geometry can generate loss of information of the interactions between components that are beyond the location of the partition.

#### 2.2 Detection using pattern recognition.

In the literature, pattern recognition for *hotspot* detection can be addressed in two ways. One of them is to represent patterns as Design Rules (DRC). The other way is to represent patterns as spatial configurations, typically as images.

Although DRC was not introduced for *hotspot* detection but to prevent the appearance of them, there are approaches that leverage the DRC characteristics to improve the accuracy in the *hotspots*-detection processes. The main objective of design-rule checking (DRC) is to achieve a high overall yield and reliability for the design. If design rules are violated, the design may not be functional. To meet this goal of improving yield, DRC has evolved from simple dimension measurement and boolean checks, to more complex rules that modify existing features, insert new features, and check the entire design for process limitations such as layer density. However, DRC is a computationally very expensive task. Usually DRC checkers will be run on each sub-section of the ASIC<sup>3</sup> to minimize the number of errors that are detected at the top level. If DRC runs on a single CPU, customers may have to wait up to a week to get the get the result for modern designs. Most design companies require DRC to run in less than a day to achieve reasonable cycle times because the DRC be likely run several times prior to the design completion. As complex conditional and recommended rules are added to compensate some deficiencies, the number of needed rules to represent a layout can result in an explosion of the rule libraries. Hence, depending entirely on DRC to detect potential *hotspots* usually slows down the design process. Even more, the systematic use of recommended rules can bring the density of a 90 nm design to the equivalent of a 130 nm design, wasting most of the benefit that a 90 nm design supposes. For this reason, the set of rules is usually relaxed and some *hotspots* can appear. However, DRC can still be useful to detect *hotspots* converting some topological characteristics of conflictive patterns into rules and then analyzing and comparing DRC logs to identify potential *hotspots* [10, 15].

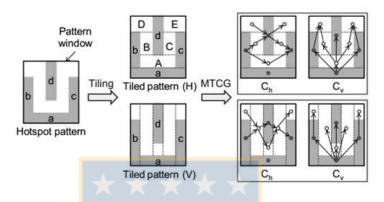

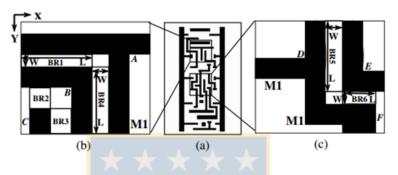

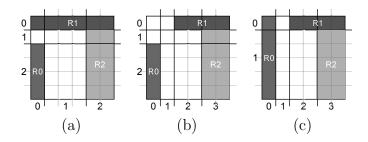

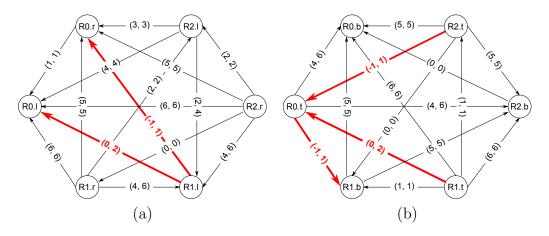

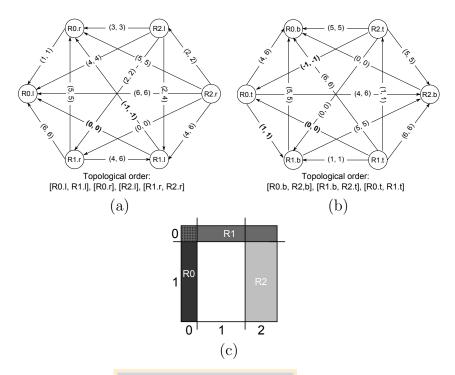

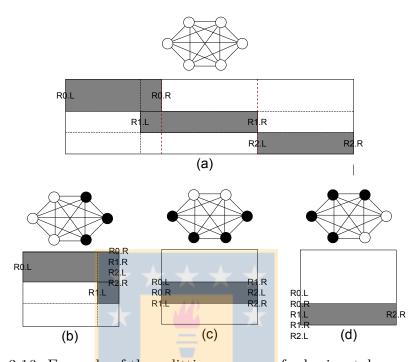

The work presented in [4] extracts topological characteristics of a certain pattern and converts them into design rules. This extraction considers different orientations of the pattern that include the four rotations  $(0^{\circ}, 90^{\circ}, 180^{\circ}, 270^{\circ})$  and the mirroring over X and Y axis, respectively. Once these critical topological features have been extracted and converted into design rules, a DRC process is applied to find regions of the design that fit the rules extracted. This occurs in two filtering stages, where the first stage indicates potential regions, while the second stage verifies the exact locations. To extract the topological relations of a pattern, they extend the representation given in [2] to obtain a modified transitive closure graph or MTCG. The original representation or TCG is used to represent compact configurations, using a pair of restriction graphs  $C_h$  and  $C_v$  (horizontal and vertical restrictions, respectively), to establish the geometric relationships. However, as we can see in figure 2.3, design patterns cannot be in a compact form because the spacing between geometries. This spacing should be considered as it is essential for the detection of *hotspots* because it also represents topological characteristics of the pattern. To properly consider these spaces in the TCG representation, the pattern is partitioned into boxes. As seen in

<sup>&</sup>lt;sup>3</sup>ASIC stands for Application Specific Integrated Circuit

figure 2.3, in the horizontal partition (Tiled pattern (H)), the horizontal edges of the geometries contained in the pattern are projected until they intersect a vertical edge of a geometry and such partition will correspond to a box (boxes a-d and A-E). The same way occurs for the vertical partitioning of the pattern, reversing the orientation of the projected geometries. So, a compact representation of the pattern is obtained, where there exist block boxes provided by the pattern geometries (a-c boxes in figure 2.3(H)) and spacing boxes (A-E boxes in figure 2.3(H)).

Figure 2.3: Construction of a MTCG graph. [4]

After the pattern has been partitioned into tiled patterns, the MTCG graph is built. Here, the vertexes represent block boxes (black dots in figure 2.3) or space boxes (white dots in figure 2.3), and the directed edges represent topological relationships between these boxes. In a horizontal contraint graph, a directed edge is added between adjacent boxes if the projection on the X-axis produces a superposition, starting from left to right. This is similar for vertical restrictions graph and the Y-axis, from the bottom to the top of the pattern.

In the first topological features extraction, lengths and widths of blocks are extracted as well as distances between two adjacent boxes and diagonal relations between two convex corners. These features are then traduced to rules, e.g., width and spacing rules shown in figure 1.2. Being written as design rules, these characteristics are expressed as inequalities.

Once the topological features of a pattern are extracted and are written as design rules, and because the representation of a pattern in MTCG is unique, the method proceeds to the verification stage. Here the extracted design rules are compared to the DRC rules under which the design was built. The idea is to determine whether any of these rules are violated. If this occurs, the location is verified in more details to see if there exists a *hotspot*. Something similar occurs in [10], where all the lengths of edges and the distances between geometries are extracted as topological features. At this analysis stage, a searching graph is built. This graph stores all the locations reported by a DRC comparison. Subsequently, the searching graph is traversed to identify potential *hotspots*.

When patterns are represented as spatial relationships for *hotspots* detection, some relevant information of conflictive patterns are usually stored in libraries. These libraries are queried to find *hotspots* occurrences scanning the whole design using pattern matching techniques. This means that these techniques have all the benefits of current pattern matching algorithms. However, even using algorithms for fuzzy geometries [6], they suffer of poor accuracy when previously unknown patterns have to be detected. Moreover, the pattern libraries can be updated to include more information about conflictive patterns as the system progresses, but as the library grows, the run-time advantages of the method decreases.

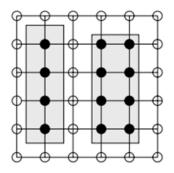

In [6], a worm-like movement is used to analyze all possible windows within a design. Each window is converted into a matrix of binary values, as shown in figure 2.4, where the value of each cell is 1 if the cell overlaps a geometry, and 0 otherwise. This process occurs in two stages, the first stage with a low resolution grid, to filter potential regions corresponding to conflicting patterns, and in a second stage with a higher grid resolution, for a more accurate analysis of selected regions at the first stage.

Figure 2.4: Binary matrix representation. [6]

For the patterns to be detected, a similar procedure is followed, with some differences. To properly handle the sizes of the libraries, a new representation called *range patterns* is introduced (see figure 2.5).

Figure 2.5: Range pattern Rocket. [6]

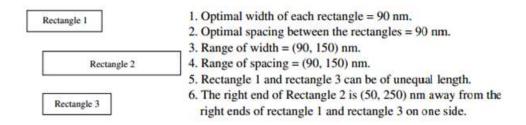

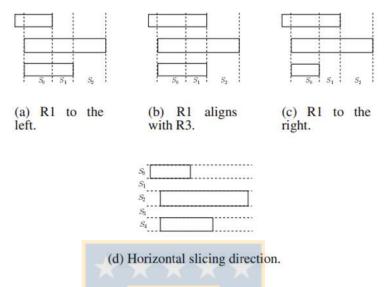

Unlike representing every possible conflicting pattern, establishing the absolute dimensions of the geometries contained in it, a *range pattern* representation allows grouping a set of patterns with similar geometries into a single pattern. This grouping occurs through the definition of ranges in the dimension of their geometries. For example, the *range pattern* in the figure 2.5 represents both the pattern for which the length of the rectangle 1 is 90nm, and the pattern for which the length of the rectangle 1 is 90nm. Without this compact representation, each of these instances of a *range pattern* should be specified independently. Explicitly listing each instance, which will be referred from now on as absolute patterns, leads us to obtain 60 different patterns from varying just one of their geometries. Thus, the representation by compacting *range patterns* allows the decrease of memory requirements for libraries in *hotspots*-detection processes. Additionally, due the characteristics of the process used for handling *range patterns*, it is possible to decrease the number of runs required to detect two absolute patterns if they belong to the same *range pattern*.

To perform the comparison of patterns, a *range pattern* should be represented in a way similar to the design representation, i.e., as a matrix representation. To achieve this, a *range pattern* is represented in what the authors call *cutting-slice* representation. For example, as shown in figure 2.6(d), to obtain the horizontal cutting-slice representation of the pattern rocket, all the horizontal edges of the geometries are projected obtaining a set of 2D matrixes. What characterizes these 2D matrixes is that, in a 2D matrix, all rows (or columns in the vertical case) are equal. The set of

2D matrixes is called cutting-slice and in a cutting-slice two adjacent slices are not equal. In figure 2.6(d) we can see that  $S_0, ..., S_4$  are horizontal slices and conform the horizontal cutting-slice of the pattern rocket. The same occurs for the vertical cutting-slice.

Figure 2.6: Cutting-slices of the rocket range pattern. [6]

Once the window is represented as a grid and the pattern as cutting-slices, both are encoded as strings to perform the first detection stage. This step compares the encoding to detect when a set of geometries within the window is similar to the geometries contained in the pattern, even when the dimensions of these geometries are not exactly the same. When a possible match is detected, the window is analyzed in a second stage where the resolution of the grid is higher, and the process takes into consideration additional information related to the dimensions of the geometries for a more accurate detection.

#### 2.3 Detection using machine learning techniques.

The techniques that use machine learning for *hotspots* detection, typically construct a classification model for patterns. Such model catalogs a pattern as *hotspots* based on the extraction of some features, and can use the classification model to predict whether future unknown patterns will give rise to *hotspots* in a certain manufacturing process. The work presented in [20] uses a machine-learning kernel (MLK) based on the extraction of critical features for *hotspot* detection. This extraction occurs in binary images that are representations of a layout. The authors propose three critical features to generate a compact representation of a certain geometrical configuration: the number of bounded rectangles (BR), T-shapes and L-shapes. This compact representation is not affected by two-dimensional transformations such as shifting, rotation or mirroring.

(a) a 45nm design, (b)(c) two examples of critical features extraction.

The bounded rectangles represent the relative geometrical positioning between adjacent components using an interval representation. For example, in figure 2.7(b) we can see that BR1, BR2, BR3 and BR4 represent de relative positioning between the components (black rectangles). Each BR is represented as a vector which codifies the parameters (W, L, (X, Y), D), where W and L are the width and the length of the bounded rectangle respectively, (X, Y) are the top-left coordinates of the rectangle, and D corresponds to the orientation of the rectangle. D is 0 when the width of the rectangle is measured along the X-axis, and 1 otherwise. On the other hand, Tshapes and L-shapes correspond to the number of shapes with a T-form or an L-form, respectively, that extend along both sides of the bounded rectangles. For example, in 2.7(b), the zone denoted as A is a T-shape for BR1 and BR4, the zone denoted as B is a L-shape for BR1, BR2, BR3 and BR4, while the zone denoted as C does not correspond to a T-shape nor a L-shape for BR2 and BR3.

In the extraction step, the binary image is partitioned in a set of binary images.

For each partition, a vector is obtained for each component within the partition. An ordered collection of vectors establish the metrics for the whole partition, which are then used as input for the MLK, iteratively creating a kernel to predict the presence of *hotspots* in future designs (note that the training of the MLK must be supervised). The MLK is based on an artificial neural network (ANN) whose objective is to minimize the squared error between the network prediction and the supervised decision. The work is used by the CALIBRE <sup>4</sup> design tool.

In [19], the authors propose a technique for *hotspot* detection that provides a full layout, feature-centric analysis. This is achieved by determining a radius of analysis, under which geometrical features are extracted (see figure 2.8). The work, which extends the work presented in [18], uses the metric features extracted from the layout not to decide whether a certain pattern is defective or not, but leaves the decision to a recursively trained and validated kernel using techniques of machine learning. This kernel, that could be based on an ANN or in a support vector machine (SVM), extends the previous work to a hierarchical learning process. The extraction process defines a radius of analysis, under which the geometries are fragmented to analyze each fragment and its neighbor fragments, defining externally and internally facing polygons.

Figure 2.8: Feature extraction. [19]

(a): Effective radious of analysis. (b): Fragmented geometries with externally and internally facing polygons.

<sup>4</sup>CALIBRE is a lithographic simulation tool of Mentor Graphics. -http://www.mentor.com.

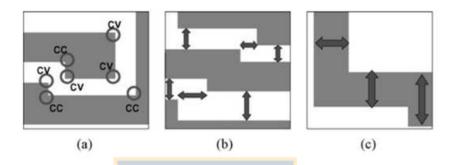

The characterization of geometries is built based on corners information (concave or convex), the distance between externally facing polygons, and the distance between internally facing polygons (see figure 2.9). This information is used to build a unidimensional vector that characterizes a fragment F. These vectors are then combined using vector operators to define a final vector  $V_f$  that characterizes the whole region of analysis. As well as the previous work, this vector  $V_f$  is invariant to rotation and mirroring, and is used as input for the SVM or ANN kernel.

Figure 2.9: Geometrical metrics. [19]

(a): Corner bases information. (b): Distance between externally facing polygons. (c): Distance between internally facing polygons.

The problem with the previous mentioned technique is that it take into account very local relations between components. Most of similar techniques use a region of analysis, so this problem could be overcome using larger regions, but this decision could increase the runtime of the process. The work presented in [23] attempts to overcome this limitation by taking into account the information of larger regions of a design, improving the execution time by using a two-level classification. The main idea of this classification is:

1. The first level uses a supervised trained classifier to separate parts of the design with potential *hotspots*. This separation is performed using information around a centric target location, e.g., geometries of the design in its vicinity. Since these near geometries have a strong influence on candidate geometries, then geometries very similar to a pattern, predefined as potential *hotspots*, will be marked at this level and will pass to the second level of the classification for a more detailed examination. 2. The second level uses as well a previously trained classifier to examine the peripheral information of the region marked as potential *hotspot* at the first level. Thus, geometries that are not in close proximity, but still have non-negligible effects on the internal geometries will be classified as *hotspots* as well. This decision occurs because as they influence the current region, marked as *hotspots*, it is desirable to remove them to not allow influencing other regions of the design.

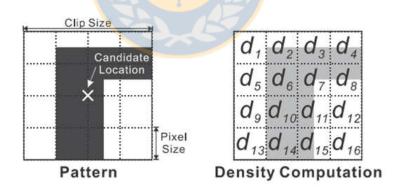

The classifiers are built using SVM, where the input vectors encode information from regions that are represented by the density of geometries that they contain. The figure 2.10 shows an example where a clip window centered at a candidate location is pixelated, and pixel densities are computed (note that the process needs at least two additional input parameters, i.e., region size and pixel size). An ordered list of density values forms the output vector. As we can see, this feature encoding step should not be confused with the actual pattern features such as convex/concave corners or line-ends. The goal of this representation is not to identify those geometrical features that may degrade the printability of a pattern. Instead, it aims to provide a compact representation of layout patterns, enabling an efficient measurement of pattern similarities for classification purposes. The SVM is the responsible to make the decision after the supervised training.

Figure 2.10: Representation based on geometries density. [23] The vector is  $[d_1, ..., d_{16}]$ .

As we can see, most of the techniques that use machine learning for detecting *hotspots* require to know the *hotspots* patterns beforehand to use them in the training

steps. While current methods demonstrate high accuracy, unknown patterns are classified as *hotspots* with a certain probability of certainty. The problem with these strategies is that for many manufacturing factories, to not properly detect the *hotspots* is not acceptable. This means long training and calibration steps, which can lead to high occurrences of false-positive errors.

#### 2.4 Graph-oriented detection.

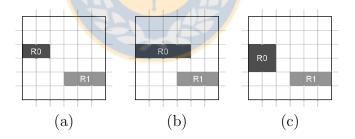

As in [4], where graphs are used to represent conflictive patterns and then these graphs are used to obtain design rules that can be used for *hotspot* detection, there are other works that use graphs with similar objectives. An example is the work presented by Kahng *et al.* in [5], where a *hotspot* filtering method derives a dual graph from an image of the pattern. The work involves the use of a graph of a certain region of the design, which reflects the variation of the critical dimensions of the geometries contained in the region. The detection is not based on the existence of patterns established as *hotspots*, but in the idea that any configuration of geometries whose interactions generate a high variation in the critical dimension (CD) could lead to the occurrence of a *hotspot*. This is similar to what occurs in the detection based on design rules, except that in this work no conditions are explicitly specified by designers. The analyzed regions are separated according to their complexity, because the greater is the complexity of the geometries that they contain, the greater is the possibility of the existence of a *hotspot*. Additionally, different types of variations in critical dimensions are separated into two types:

- 1. CD variations induced by corners, where two orthogonal geometries connected as a corner may vary as corner-rounding (see figure 2.11(a)).

- 2. CD variations induced by the proximity between geometries, where two very close geometries can suffer necking or bridging (see figure 2.11(b)-(c)).

Figure 2.11: CD variations induced by the interaction between geometries. [5]

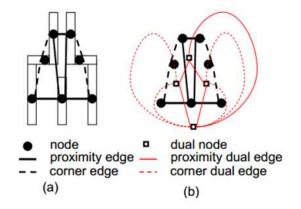

The first stage of the process is to build a graph G for regions of the design that reflects the CD variations induced by the geometries contained in the region. Given a design region L, the design graph  $G = (V, E_c \cup E_p)$  consists of nodes V, corner edges  $E_c$ , and proximity edges  $E_p$ .

- 1. For each horizontal and vertical geometry, a node  $v \in V$  is created.

- 2. For two orthogonal geometries connected, the corresponding nodes are connected by an edge  $e \in E_c$ , where the weight of the edge is a constant.

- 3. A proximity edge  $e \in E_p$  is created between two nodes if the corresponding geometries are adjacent and have the same orientation. The weight of the edge reflects the separation between the geometries and the overlap of the width or length projections.

Figure 2.12(a) shows an example of a region which contains 7 nodes representing 7 geometries, 4 corners (dotted lines) and 5 proximities (solid lines).

Figure 2.12: Graph and dual graph representation. [5]

The second stage consists in the planarization of the graph and obtaining its dual graph. Thus, the graph  $G = (V, E_c \cup E_p)$  is converted to its dual  $G^D = (V^D, E_c^D \cup E_p^D)$ . The dual graph  $G^D$  of a graph G is constructed by representing each face f of G with a dual node n, which is the sum of the weights of the edges forming f. An edge ethat belongs to two faces  $f_1$  and  $f_2 \in G$  is represented with a dual edge  $e^d = \{n_1, n_2\}$ in  $G^D$  with the same weight of e. As the dual graph  $G^D$  exists if G is planar, that is, there are no edges that intersect, for each edge that does not fulfill the condition, the less weighted edge is eliminated. Finally the detection of *hotspots* occurs in three levels, by using a lookup table with weight values that are considered for potential CD variations. The detection at the dual graph edges level detects the *hotspots* caused by two close geometries or two geometries connected as corners. Face-level detection finds *hotspots* produced by several close geometries. Finally, the merged-face level detection finds *hotspots* produced by complex relationships between geometries. To do so, once the dual graph  $G^D$  is built, its nodes are sorted by their weights. Then, the sorted nodes that share the same geometries are merged, which means to merge the faces in G. This detection level is based on the idea that a *hotspot* is a combination of various local "bad" geometric configurations. Assuming that the effect on the CD variation is accumulative, this effect may by reflected by the weight of a dual node, that is, the total weight that conforms the face in G. However, a hotspot can be produced by more complex relationships between geometries that belong to different faces. For this reason, the authors consider merging nodes of the dual graph and running a detection on this merging.

## Chapter 3

## Signature-based indexing and searching.

Unlike previous work in *process-hotspot* detection that uses complex features in the process of *hotspot* detection, we propose to pre-process layouts in order to extract signatures that characterize windows within the layouts. The idea is to use these signatures to filter out portions of the layout that could be excluded from the *hotspot*-detection process, reducing the costs and efforts needed to detect the occurrence of *hotspots*. The *signature* can be used as search criteria and, therefore, be organized in an index structure. To illustrate the usefulness of the *signature*, we consider a patternmatching process where the signatures of a set of patterns can be used as search keys of an index structure to return only possible layout's windows that should be analyzed in a *hotspot*-detection process.

This work presents a *signature* for 2D spatial configurations as a pair of vectors of numbers representing changes between geometries and empty-spaces along the horizontal and vertical slices of a configuration. As the *signature* should be general enough to consider different possible patterns, we consider the representation of *range patterns* as in [6], which enables a compactly representation of similar exact patterns. Using this representation, a method extracts signatures from *range patterns*, and then use these signatures as search criteria over the inverted index to retrieve candidate windows that can match the patterns. The main difference with respect to our previous work is that the candidate searching can be done even if the layout's windows from where the *signature* are extracted are not of the same size of the pattern realization. Here, a pattern realization is understood as a specific geometrical configuration in the space that a *range pattern* specification can generate. Also, as additional contribution, a detailed analysis is executed for each element involved in the implementation of the theoretical work (e.g., extraction method, data storing structure, and so on) comparing different decisions. In summary, the key contributions presented in this chapter are:

- Definition of a *signature* for configurations composed of non-overlapping rectangles.

- Implementation of algorithms for the extraction of the *signature* from layouts by windows and from *range patterns*.

- Use of the *signature* with an indexing structure to efficiently search for candidate windows that can match a *hotspot* pattern.

# 3.1 Signature.

As we have said, the filtering-out of layout portions is based on the use of a signature. What is a signature? In this work, a signature is a mapping from a geometric configuration composed of non-overlapping rectangles to one or more numbers. Unlike signatures characterizing single shapes such as those in [17] and [21], a signature here has to characterize a set of shapes (rectangles). This set of shapes will represent a set of IC components that in a design appear as rectangular shapes. So, a simple but effective signature that characterizes two-dimensional configurations composed of non-overlapping rectangles located along or perpendicular to x- or y-axis is introduced.

To formalize this *signature*, we first define the concepts of grid and slices of a representation of two-dimensional configurations.

**Definition 1**  $A \ N \times M$  regular grid representation of a configuration of rectangular shapes (e.g. a set of IC components) is composed by  $N \times M$  of cells of the same size in a two-dimensional space, such that there exist N horizontal units and for each of these N units, there exist M cells along the horizontal axis.

The granularity of this representation is such that a cell of the grid overlaps a rectangle (and have a value of 1), or it do not overlaps a rectangle at all (and have a value of 0). Simplifying the concept, we can say that a regular grid representation

of a configuration is a binary-cell matrix, where all the cells are squares of the same size (i.e. the width and the height of each cell is the same), and correspond to the design resolution (i.e. the minimum printable element).

Additionally to the regular grid representation, we have an irregular grid representation. This irregular grid representation is based on grid slices, which are defined as follows:

**Definition 2** Horizontal(vertical) slice of a regular grid representation is a set of contiguous horizontal(vertical) cells (rows or columns, respectively) of the regular grid that are equal. Each slice contains a number of fragments that group equal cells in the orthogonal axis (a fragment can be conceived as a sub-matrix where all the cells have the same value).

With the previous defined concepts, we can define the last concept called cuttingslice.

**Definition 3** A cutting-slice is a set of horizontal or vertical slices  $\{S_0, \ldots, S_{n-1}\}$  that meets the following specifications:

- 1. Adjacent slices are not equal, i.e.  $S_i \neq S_{i+1}$ ,  $0 \leq i \leq (n-2)$

- 2. Each slice  $S_i$  is decomposed into fragments  $\{F_{i,0}, \ldots, F_{i,m-1}\}$ , where  $F_{i,j} \neq F_{i,j+1}, 0 \leq j \leq (m-2)$

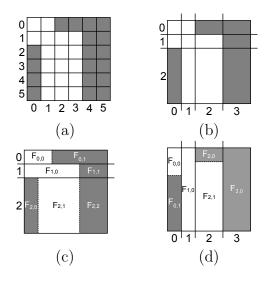

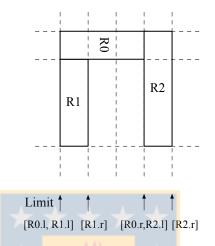

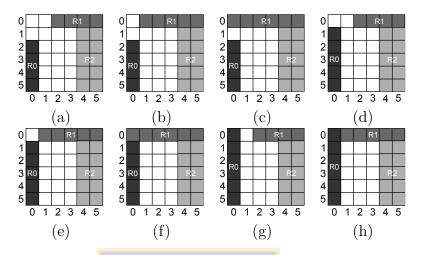

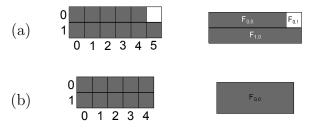

Thus, the irregular grid representation is defined as the representation formed by the pair of horizontal and vertical cutting-slices of a regular grid representation. Figure 3.1 shows and example of the different representations of a simple configuration.

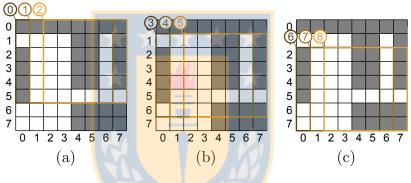

Figure 3.1: Regular and irregular grid representation.

In figure 3.1(a) we can see a regular representation of a  $6 \times 6$  simple configuration. There, all the cells are squares of the same size, and the size of the each cell is the minimum size (length or width) of a shape. Figure 3.1(b) shows the irregular representation of the same configuration. Here, we can notice that the 4<sup>th</sup> and 5<sup>th</sup> columns in figure 3.1(a) are merged into the 3<sup>rd</sup> column in figure 3.1(b) because both columns are equal. The same occurs to the 2<sup>nd</sup> to 5<sup>th</sup> rows in figure 3.1(a), that are merged into the 2<sup>nd</sup> row in figure 3.1(b). Note that, if not all the rows from the 2<sup>nd</sup> to 5<sup>th</sup> in figure 3.1(a) were merged into a single one row, we would have two horizontal slices in the irregular grid representation that would be equal, and would not satisfy the cutting-slice specifications.

Using the previous definitions, we can proceed to define the *signature* as it follows:

**Definition 4** Given and  $N \times M$  grid representation of a two-dimensional configuration of non-overlapping rectangles, the change-based signature ( $S^+$ ) is a tuple of the form ( $[h_0, \ldots, h_N]$ ,  $[v_0, \ldots, v_M]$ ), where  $h_i$  ( $0 \le i \le N$ ) is the number of changes of values along the horizontal slice i and  $v_j$  ( $0 \le j \le M$ ) is the number of changes of values along the vertical slice j.

Here, a change of value ocurrs when, given a cell in a slice, the adjacent cell has the opposite value (i.e., 0 to 1, or 1 to 0). For example, in the slice [1, 0, 1] we have 2 changes of values; 1 to 0 (0<sup>th</sup> to 1<sup>th</sup> position) and then 0 to 1 (1<sup>th</sup> to 2<sup>nd</sup> position).

Notice that the definition of  $S^+$  applies to grid representation, and therefore, to regular and irregular representations. In what follows, and unless the contrary is explicitly stated,  $S^+$  will refer to the *signature* over irregular grid representations.

Using figure 3.1(b) as an example, we can see that its  $S^+$  is the tuple ([1, 1, 2], [1, 0, 1, 0]). Figure 3.1(c) and (d) shows us the horizontal and vertical slices, respectively, each of them with its corresponding fragments. As an example,  $F_{0,0}$  corresponds to the fragment 0 of the 0<sup>th</sup> horizontal slice, which corresponds to a two-cell block in the corresponding regular grid representation (the cell at (0,0) and the cell at (0,1) in figure 3.1(a)).

It is important to note that  $\mathcal{S}^+$  has the following properties:

- $S^+$  is scale independent when extracted from an irregular grid representation. It is easy to see that  $S^+$  will not change as we apply a continuous scaling over the whole configuration, because equal rows or columns are represented by a single slice. Even more,  $S^+$  will be the same for patterns that are similar but differ in the distance and the width of rectangles. As an example, if the width of the 1<sup>th</sup> vertical slice in figure 3.2(d) was wider, the vertical part of the  $S^+$ tuple would even be [1, 0, 1, 0].

- The number of changes along a slice is equivalent to the number of fragments in the slice minus 1.

# 3.2 Design layout representation and signature extraction.

A design layout is a computational representation of a design, which specifies the organization of electronic components of an IC. In Chapter 2, we have seen that, for manufacturing purposes, what really matters is to produce a mask from a design. From now, we will refer to this mask as the layout, or what the layout represents, i.e., a set of geometrical elements. These representations are typically stored in the industry as GDSII format files that are constructed using CAD tools and could represent a chip area range from a few square millimeters to around 450  $mm^2$  using from few GBs up to 100GB of space.

In this work, and similarly to [6], a layout is represented by a  $N \times M$  regular grid L, denoted by  $L_{N \times M}$ , where N and M depend on the granularity of the layout representation, which is typically equal to the manufacturing grid size. This manufacturing grid size depends on the manufacturing technology, and decreases each year until the current 25nm technology. Each element L[i, j], with  $0 \le i \le N$  and  $0 \le j \le M$  is associated with a spatial location in the manufacturing grid, such that L[i, j] = 1 if there exists a rectangle that overlaps this location, and L[i, j] = 0, otherwise.

Figure 3.2 shows a simple example of a layout representation using the same configuration used previously. Similar to what occurs in Chapter 3.1, the granularity of the grid is such that each cell represents the minimum size of any unit in the layout, so that a cell overlaps a rectangle or it does not overlap any rectangle at all.

Figure 3.2: Example of a layout representation

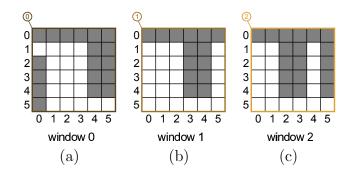

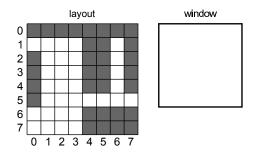

The  $N \times M$  regular grid L representing a layout is pre-processed by windows in an off-line process applied previously to the *hotspot* detection step. These windows are then mapped to irregular grids to extract  $S^+$ . A window corresponds to a rectangular sub-portion of the layout and is defined as a  $N' \times M'$  sub-grid W of L, denoted by  $W_{N' \times M'}$ , with  $1 \leq N' \leq N$  and  $1 \leq M' \leq M$ , and where rows (and columns) are consecutive in L.

The signature extraction process starts with a window located at the top-left corner of the layout grid. Without changing the window dimensions, the window slides one-by-one position along the x-axis and then along the y-axis. Thus, given a layout grid of size  $N \times M$  and a window size of  $N' \times M'$ , the number of windows in the layout is  $(N-N'+1) \times (M-M'+1)$ .

Windows are identified by using a correlative number following the window sliding. There exists a direct mapping from this ID to the initial coordinates (top-left corner) of the window in the layout. Given a layout  $L_{N\times M}$ , windows of size  $N' \times M'$ , and a number *i* representing the correlative window incremented by sliding the window horizontally and then vertically, coordinates for the top-left corner of the window are  $(i/(M-M'+1), i \mod (M-M'+1))$ . Conversely, given a coordinate pair (x, y) for the top-left corner of a window, its ID *i* is  $(y \times (M - M' + 1)) + x$ .

For each window, the horizontal and vertical slices are determined and  $\mathcal{S}^+$  is extracted from the irregular-grid representation of the window by using the following algorithm.

| <b>Algorithm 1</b> Generates the $\mathcal{S}^+$ of a layout window.                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>Input</b> <i>layout</i> : A layout in binary grid representation, $x, y$ : (x, y) coordinates of the window, <i>width</i> : window's |

| width, <i>height</i> : window's height.                                                                                                 |

| <b>Output</b> signature : The signature of the window as a pair of lists: (horizontal_changes, vertical_changes).                       |

| 1: $signature \leftarrow empty pair$                                                                                                    |

| 2: $horizontal\_signature \leftarrow empty list$                                                                                        |

| 3: for $j = 0$ to (height-1) do                                                                                                         |

| 4: $equal\_next\_row \leftarrow TRUE$                                                                                                   |

| 5: $changes \leftarrow 0$                                                                                                               |

| 6: $last\_value \leftarrow layout[y + j][x]$                                                                                            |

| 7: for $i = 0$ to (width-1) do                                                                                                          |

| 8: <b>if</b> $layout[y+j][x+i] \neq last_value$ <b>then</b>                                                                             |

| 9: $changes \leftarrow changes + 1$                                                                                                     |

| 10: $last\_value \leftarrow layout[y+j][x+i]$                                                                                           |

| 11: if $layout[y+j][x+i] \neq layout[y+j+1][x+i]$ then                                                                                  |

| 12: $equal\_next\_row \leftarrow FALSE$                                                                                                 |

| 13: if (not equal_next_row) $\lor$ (j = (height-1)) then                                                                                |

| 14: $horizontal\_signature \leftarrow Append changes$                                                                                   |